类别:其他 出处:网络整理 发布于:2024-09-05 17:17:40 | 79 次阅读

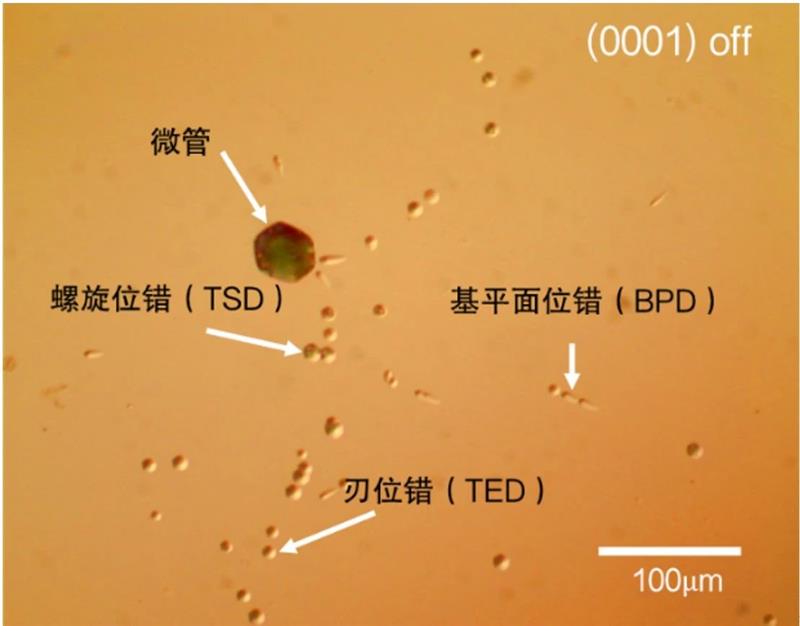

图1显示了通过熔融KOH对8°偏角(0001)4H-SiC衬底的表面进行蚀刻,在晶体缺陷部分形成凹坑的显微镜照片。位错线在垂直于表面的方向上延伸,反映了晶体的对称性,蚀刻后出现六角形的凹坑。另一方面,基面位错在(0001)面(与表面平行的方向),位错线朝不同方向延伸,形成的凹坑呈椭圆形。在螺旋位错中存在多个晶体偏移大小不同的位错。晶体偏移较大的螺旋位错和混合位错会在器件中产生漏电流。对于小型位错,大多数不会影响器件性能。

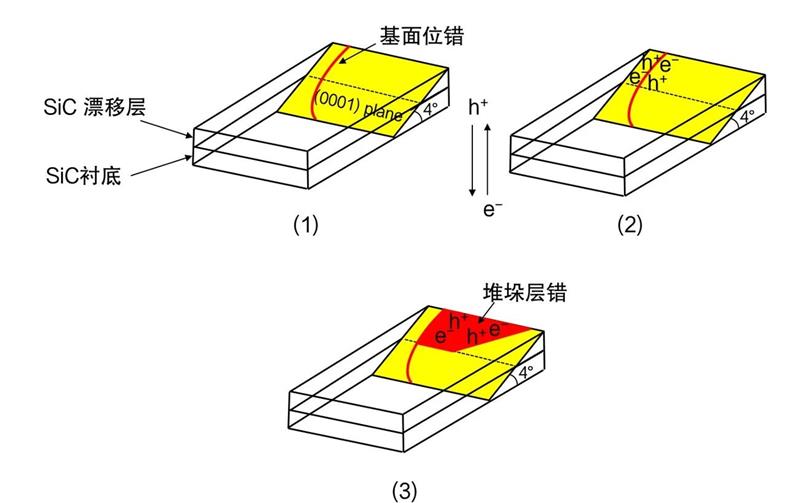

(1)存在于SiC衬底中的基面位错也延伸到漂移层中。(2)当双极性电流流过时,漂移层中的电子和空穴被基面位错俘获。(3)被俘获的电子和空穴复合并释放能量。释放的能量导致部分位错移动,移动的部分形成堆垛层错,堆垛层错区域进一步俘获电子和空穴,导致部分位错的继续移动(堆垛层错区域扩展)。形成堆垛层错的区域起到高电阻区域的作用。

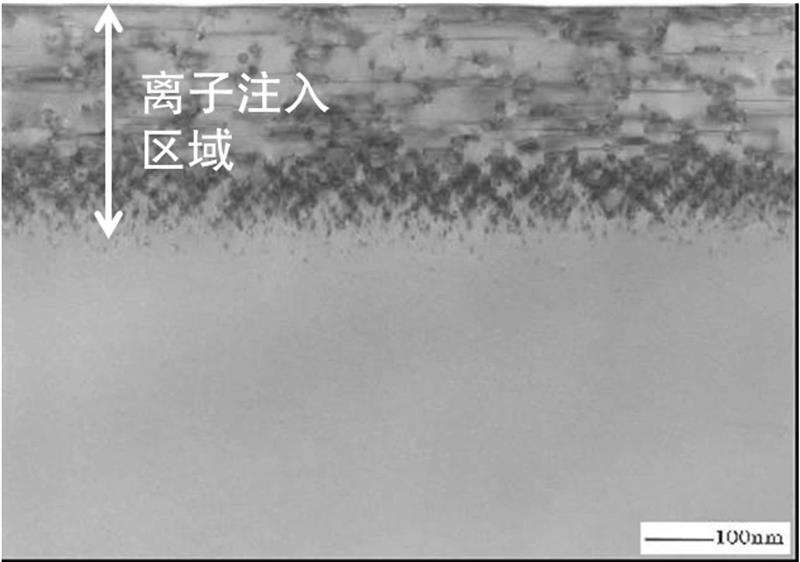

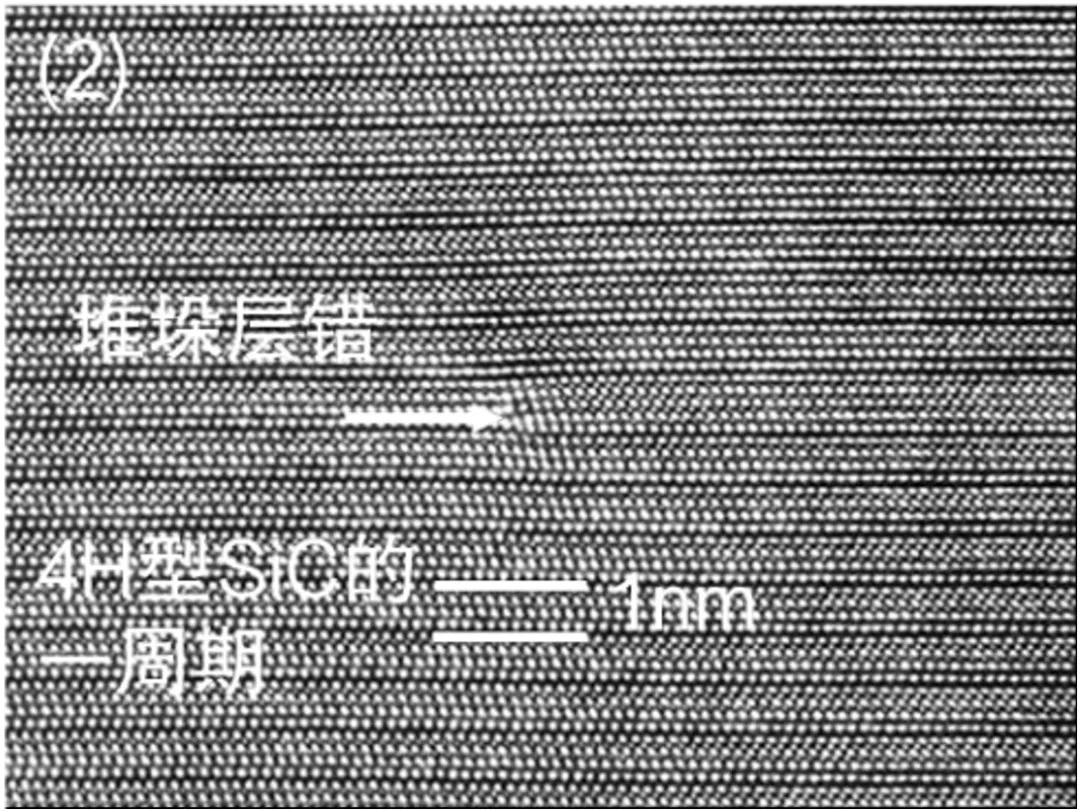

在对SiC进行离子注入时,会产生晶体缺陷。图3、图4展示了对SiC进行高浓度Al离子注入后再退火的横截面TEM(透射电子显微镜)图像。从图3中可以看出,注入Al的区域存在着高密度因变形而看起来黑色的缺陷。即使经过高温退火,晶体仍未完全恢复。在图4中,放大了缺陷部分,展示了高分辨率TEM图像(晶格图像)。可以观察到每4层构成一个周期(周期为1纳米)的结构,表明这是4H-SiC。图中箭头所指位置插入了一层多余的层,形成了Frank堆垛层错。关于这一部分,已知注入的元素Al等以层状方式聚集,形成堆垛层错。

图3:由于离子注入而形成晶体缺陷的TEM图像

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。